Circuit

- class ipkiss3.all.Circuit

A PCell which derives its layout, netlist and model from a set of specifications in order to create a circuit.

Pre-defined instances of which the circuit is composed are specified as a dictionary insts. (This excludes connecting waveguides generated on the basis of the routing specifications).

Placement and routing is done with

i3.place_and_routeusing a combination of place_specs and route_specs (specifications as in Placement and Routing Reference).Ports are exposed using

i3.expose_portsusing port_specsThe netlist and circuit model views are derived from the layout using netlist extraction.

Create a single design by instantiating i3.Circuit directly, or create a parametric circuit by inheriting from it.

- Parameters:

- strict:

If True, any error will raise an exception and stop the program flow. If False, any routing error will give a warning and draw a straight line on an error layer. See

i3.ConnectLogicalfor more information.- exposed_ports: ( dict ), *None allowed*

Ports to be exposed, mapping {‘instance_name:port_name’: external_port_name’} map for i3.expose_ports().Set to None (default) to expose all unconnected ports

- specs: list

Placement and routing specifications

- insts: ( OrderedDict and key: str, value: PCell, _View ), *None allowed*

Instances of child cells which this circuit is composed of: {‘instance_name’: cell, …} where cell is an i3.PCell object.

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

Warning

The insts property of Circuit contains the instances specified by the user, while the instances property of the Layout view contains the full set of instances including connecting waveguides.

Notes

The following 2 are largely equivalent (you can also navigate to i3.Circuit in your code editor to see the exact behavior):

class MyCircuit(i3.Circuit): def _default_specs(self): return my_specs def _default_exposed_ports(self): return my_exposed_ports class MyCircuit(i3.PCell): class Layout(i3.LayoutView): def generate(self, layout): layout = i3.place_and_route(layout=layout, specs=specs) layout += i3.expose_ports(layout, my_exposed_ports) return layout class Netlist(i3.NetlistFromLayout): pass class CircuitModel(i3.CircuitModelView): def _generate_model(self): return HierarchicalModel.from_netlistview(self.netlist_view)

Circuitprovides a convenient standardized workflow for creating specification-based layout-driven circuits. When more flexibility is needed, inherit from i3.PCell instead. Changing from i3.Circuit to i3.PCell is done as in the example above.Examples

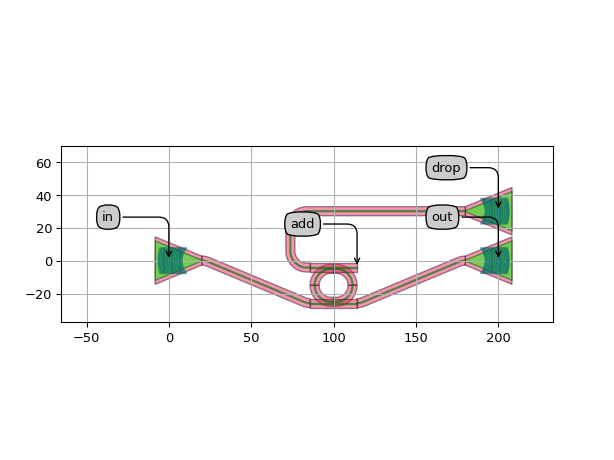

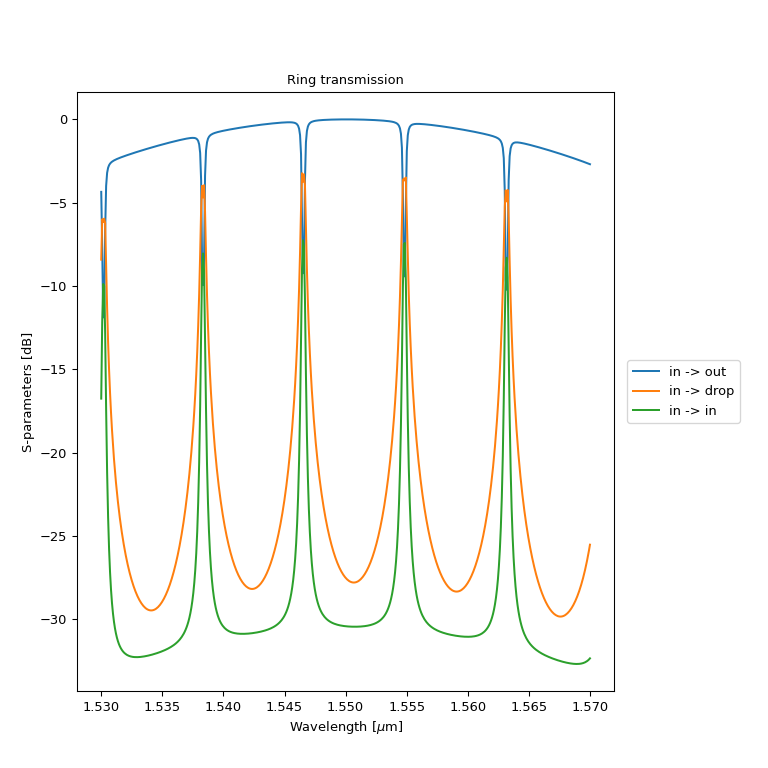

import numpy as np import si_fab.all as pdk # noqa: F401 import ipkiss3.all as i3 from picazzo3.fibcoup.curved import FiberCouplerCurvedGrating from picazzo3.filters.ring import RingRect180DropFilter # waveguide template waveguide_template = pdk.SiWireWaveguideTemplate() waveguide_template.Layout(core_width=0.5, cladding_width=5.5) # instances fibcoup = FiberCouplerCurvedGrating(start_trace_template=waveguide_template) coupler_parameters = dict( cross_coupling1=1j * 0.0784**0.5, straight_coupling1=0.9216**0.5, reflection_in1=1j * 0.030 ) ring = RingRect180DropFilter( ring_trace_template=waveguide_template, coupler_trace_templates=[waveguide_template, waveguide_template] ) ring.Layout(bend_radius=10.0, straights=[3.0, 0.0], coupler_spacings=[0.8, 0.8]) ring.CircuitModel(coupler_parameters=[coupler_parameters, coupler_parameters]) fc_spacing = 200.0 ring_test_site = i3.Circuit( specs=[ i3.Inst(["fc_in", "fc_out", "fc_drop"], fibcoup), i3.Inst("ring", ring), i3.Place("fc_in:vertical_in", (0.0, 0.0)), i3.Place("fc_out:vertical_in", (fc_spacing, 0.0)), i3.FlipH("fc_out"), i3.Place("fc_drop:vertical_in", (fc_spacing, 30.0)), i3.FlipH("fc_drop"), i3.Place("ring", (0.5 * fc_spacing, -15.0)), i3.ConnectBend([("fc_in:out", "ring:in1"), ("fc_out:out", "ring:out1")], bend_radius=10), i3.ConnectManhattan("fc_drop:out", "ring:out2", bend_radius=10), ], exposed_ports={ "fc_in:vertical_in": "in", "fc_out:vertical_in": "out", "fc_drop:vertical_in": "drop", "ring:in2": "add", }, ) ring_test_layout = ring_test_site.Layout() ring_test_layout.visualize(annotate=True) sim_wavelengths = np.linspace(1.53, 1.57, 500) ring_cm = ring_test_site.CircuitModel() s_mat = ring_cm.get_smatrix(sim_wavelengths) s_mat.visualize(term_pairs=[("in", "out"), ("in", "drop"), ("in", "in")], scale="dB", title="Ring transmission")

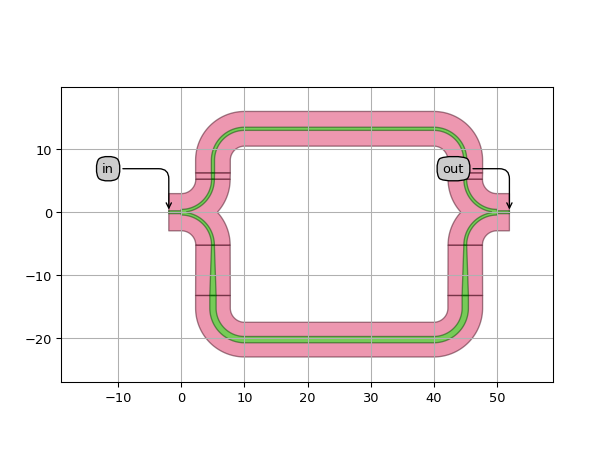

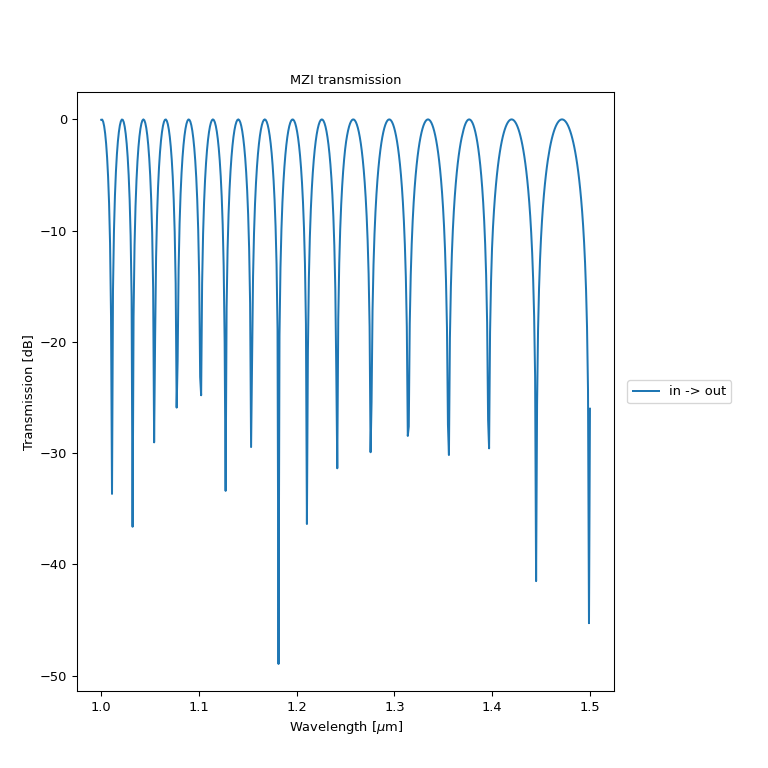

import numpy as np import si_fab.all as pdk # noqa: F401 import ipkiss3.all as i3 from picazzo3.wg.splitters import WgYCombiner, WgYSplitter # waveguide templates for MZI arms wg_t_arm1 = pdk.SiWireWaveguideTemplate() wg_t_arm1.Layout(core_width=1.0, cladding_width=5.5) wg_t_arm2 = pdk.SiWireWaveguideTemplate() wg_t_arm2.Layout(core_width=0.5, cladding_width=5.5) mzi = i3.Circuit( specs=[ i3.Inst("splitter", WgYSplitter()), i3.Inst("combiner", WgYCombiner()), i3.Place("splitter", (0, 0)), i3.Place("combiner", (50, 0), relative_to="splitter"), i3.ConnectManhattan("splitter:arm1", "combiner:arm1", "arm1", trace_template=wg_t_arm1), i3.ConnectManhattan("splitter:arm2", "combiner:arm2", "arm2", trace_template=wg_t_arm2), ], exposed_ports={ "splitter:center": "in", "combiner:center": "out", }, ) mzi_layout = mzi.Layout() mzi_layout.visualize(annotate=True) sim_wavelengths = np.linspace(1.0, 1.5, 500) mzi_cm = mzi.CircuitModel() s_mat = mzi_cm.get_smatrix(sim_wavelengths) s_mat.visualize(term_pairs=[("in", "out")], scale="dB", title="MZI transmission", ylabel="Transmission [dB]")

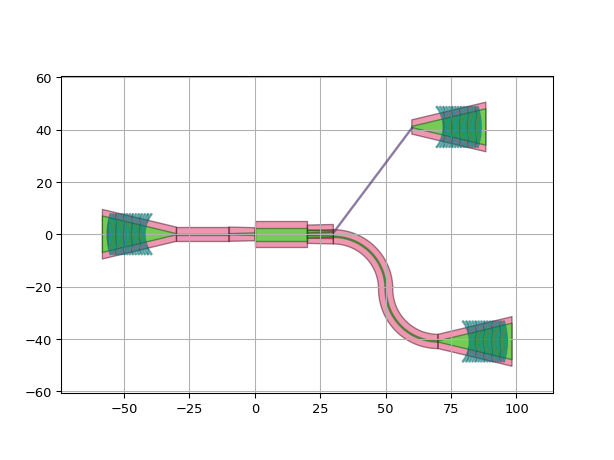

import si_fab.all as pdk # noqa: F401 from ipkiss3 import all as i3 from picazzo3.fibcoup.curved import FiberCouplerCurvedGrating from picazzo3.filters.mmi.cell import MMI1x2Tapered # Create the template for the MMI mmi_trace_template = pdk.SiWireWaveguideTemplate() mmi_trace_template.Layout(core_width=5.0, cladding_width=10.0) mmi_access_template = pdk.SiWireWaveguideTemplate() mmi_access_template.Layout(core_width=1.0, cladding_width=5.0) mmi = MMI1x2Tapered( mmi_trace_template=mmi_trace_template, input_trace_template=mmi_access_template, output_trace_template=mmi_access_template, trace_template=i3.TECH.PCELLS.WG.DEFAULT, ) mmi.Layout(transition_length=10.0, length=20.0, trace_spacing=2.0) # Create the template for the grating couplers end_wg_tmpl = pdk.SiWireWaveguideTemplate() end_wg_tmpl.Layout(core_width=10.0, cladding_width=2 * i3.TECH.WG.TRENCH_WIDTH + 10.0) coupler = FiberCouplerCurvedGrating( start_trace_template=i3.TECH.PCELLS.WG.DEFAULT, wide_trace_template=end_wg_tmpl ) coupler.Layout(period_x=1.0, focal_distance_x=20.0) # Place and route the MMI and grating couplers circuit = i3.Circuit( specs=[ i3.Inst(["coupler_in", "coupler_out1", "coupler_out2"], coupler), i3.Inst("mmi", mmi), i3.Place("mmi", (0, 0)), i3.Place("coupler_in", (-50, 0), relative_to="mmi"), i3.Place("coupler_out1:out", (40, -40), relative_to="mmi:out1"), # Place ports too close together for bend_radius=20: i3.Place("coupler_out2:out", (30, 40), relative_to="mmi:out2"), i3.FlipH(["coupler_out1", "coupler_out2"]), i3.ConnectBend( [("coupler_in:out", "mmi:in"), ("mmi:out1", "coupler_out1:out"), ("mmi:out2", "coupler_out2:out")], bend_radius=20, ), ], strict=False, # Will draw a straight line on an error layer ) lv = circuit.get_default_view(i3.LayoutView) lv.visualize()

i3.place_and_route and i3.Circuit can also be used to place and route electrical components:

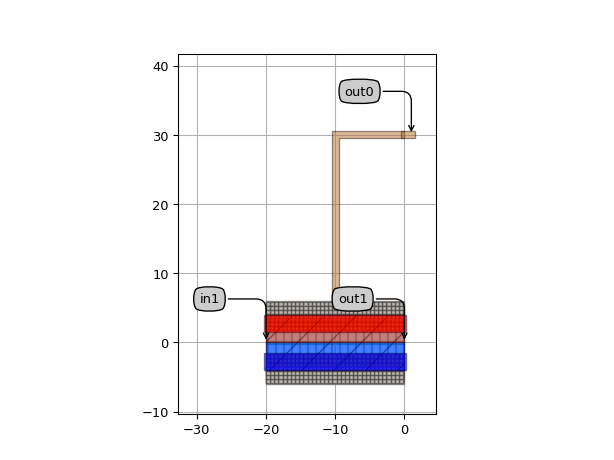

"""An important requirement when using i3.Circuit and i3.place_and_route is that the ports should have an angle. For optical ports, this will always be the case. For electrical ports, however, the angle is not always specified. In this example, we'll extend ElectricalWire and PhaseShifterWaveguide to specify the angles on its electrical ports. We'll also make sure the metal layers match as this is required by ConnectElectrical if no VIAs are used. """ import si_fab.all as pdk # noqa: F401 import ipkiss3.all as i3 layer = pdk.PhaseShifterWaveguide().Layout().ports["in"].layer class ElectricalWire(i3.ElectricalWire): class Layout(i3.ElectricalWire.Layout): def _generate_ports(self, ports): ports = super()._generate_ports(ports) angles = self.shape.angles_deg() in_angle, out_angle = angles[0] + 180, angles[-1] ports["in"].angle = in_angle ports["out"].angle = out_angle ports["in"].layer = layer ports["out"].layer = layer return ports class PhaseModulator(pdk.PhaseShifterWaveguide): class Layout(pdk.PhaseShifterWaveguide.Layout): def _generate_ports(self, ports): ports = super()._generate_ports(ports) ports["anode"].angle = 90 ports["cathode"].angle = -90 ports["anode"].layer = layer ports["cathode"].layer = layer return ports wire = ElectricalWire() phmod = PhaseModulator() phmod.Layout(length=20) circuit = i3.Circuit( specs=[ i3.Inst("wire", wire), i3.Inst("modulator", phmod), i3.Place("modulator:out", (0, 0)), i3.Place("wire:in", (0, 30)), i3.ConnectElectrical("modulator:anode", "wire:in"), ], exposed_ports={ "wire:out": "out0", "modulator:out": "out1", "modulator:in": "in1", }, ) lay = circuit.Layout() lay.visualize(annotate=True)

Views

- class Layout

- Parameters:

- view_name: String that contains only alphanumeric characters from the ASCII set or contains _$. ASCII set is extended on PY3.

The name of the view