Luceda PDK for CORNERSTONE SiN

The Luceda PDK for CORNERSTONE SiN allows to design and tape out to CORNERSTONE SiN process.

Regarding CORNERSTONE SiN process, additional information can be found here.

Contents

PDK Documentation

This document explains how to use the Luceda Process Design Kit (PDK) for CORNERSTONE SiN (version 1.1.luceda3).

The PDK can be used from Luceda IPKISS, providing the following functionality:

definition and layout of circuits using CORNERSTONE’s predefined library of cells (building blocks), which is entirely available within IPKISS,

waveguide routing using the waveguide types defined by CORNERSTONE, or custom defined waveguides following CORNERSTONE design rules,

definition of custom devices using CORNERSTONE layers and design rules,

simulation of custom devices using IPKISS’ built-in solvers and interfaces to 3rd party tools such as Dassault Systems CST Studio Suite and Lumerical FDTD Solutions,

circuit editing from Siemens L-Edit using Luceda Link for Siemens EDA.

This document explains how to get started with the PDK, lists the cells that are available and documents the technology for custom design.

Changelog

This changelog shows the changes in the Luceda PDK for CORNERSTONE SiN.

1.1.luceda3

Fixed the grating couplers to work with Luceda 3.10 and 3.11. Don’t use the PDK with Luceda 3.9 anymore.

1.1.luceda2

Fixed MMI 2x1 model

Added an .iclib file (library file recognized by IPKISS Canvas) with symbol drawings

1.1.luceda1

Updated for IPKISS 3.9. The PDK runs on Python3 as well as Python2 IPKISS 3.9 is required to run the PDK

1.1

Updated for IPKISS 3.7

1.0.0

Initial Luceda PDK for CORNERSTONE SiN release:

Technology settings, drawing layers, GDSII, IPKISS Link for Siemens EDA compatibility, virtual fabrication

Waveguides, MMI and grating coupler building blocks

Introduction

Process Design Kit (PDK) based design concept

If you already know about Process Design Kits (PDKs) in general, please skip to the section Getting started.

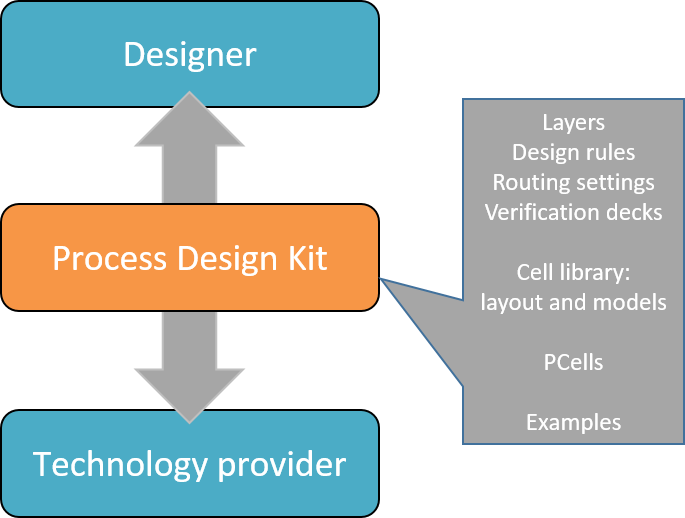

A PDK helps to bridge the gap between the fab or foundry offering IC technology and the designer who creates an IC design in that technology, as shown by Figure 1. In order to create a design, the designer needs to have the library cells created by the fab available, as well as technology details required for custom design of components. A PDK is implemented for a specific set of software tools.

Fig. 1 Concept of a Process Design Kit (PDK)

Luceda develops such a PDK so that it can be used by the Luceda tools (Luceda Link for Siemens EDA or Luceda IPKISS).

Luceda PDK has several components:

Technology settings that allow for custom design:

Layers to draw with, in accordance with the foundry’s definitions.

Design rules, which provide dimensional constraints for the design to be manufacturable.

A design rule checking (DRC) deck, checking that the designer’s mask layout adheres to the foundry’s design rules.

A technology description that allows to generate 2D and 3D models that can be sent to physical simulation tools such as for FDTD or mode propagation.

Routing settings for optical waveguides and electrical wiring

The fab’s cell library, providing validated building blocks to the designer:

Layout models that allow to place and connect the cells in the layout. These can be ‘black-box’: the detailed layout may not be visible, only the optical and electrical I/O and the bounding box.

Simulation models that allow for simulation and functional verification of a circuit based on these cells.

Parametric cells for typical complex cells or repetitive tasks that a designer would like to do

Examples and (this) manual to get started

The combination of Luceda’s design software and the Luceda PDK for CORNERSTONE SiN is what enables the designer to create a design specific for the CORNERSTONE SiN technology.

Note

In this text, the words cell, component and building block are used interchangeably. In the context of a PDK, a cell, building block or component usually delivers a specific unit function, such as a fiber coupler, splitter or phase modulator. There could also be more complex cells in the PDK library though. In the context of the user design, cell could mean any design or hierarchical part thereof.

Use case: PDK cell library based design

The Luceda PDK for CORNERSTONE SiN provides a library with a number of predefined cells for the C band (1550nm) and O band (1310nm). With this library available from IPKISS, the designer can create a circuit directly in code (IPKISS) or from the L-Edit GUI using drag-and-drop of devices from the library (IPKISS Link for Siemens EDA). After placing the PDK cells, optical waveguides can be drawn in a manual or semi-automated fashion. In addition, the PDK provides the necessary settings to use picazzo, Luceda’s pcell template library with functions like ring resonators, MMIs, modulators, Mach-Zehnder interferometers, fanouts, and many more.

This approach allows for fast prototyping of designs using the CORNERSTONE SiN technology.

Use case: Custom cell design

In a lot of cases, the user will want to design custom components and include them in the design. IPKISS provides several functions for that purpose:

Parametric cells can be defined fully in Python script, with their parameters (properties in IPKISS), layout and simulation model.

Basic building blocks can be virtually fabricated and sent to electromagnetic simulation tools such as FDTD and EME. IPKISS has a built-in mode solver CAMFR and provides interfaces to CST Studio suite and other 3rd party tools.

More complex subcircuits defined in IPKISS can be simulated using the built-in compact model solver Caphe. The designer can provide models for the basic building blocks, or generate them from simulation or measurement data.

The designer can maintain the resulting parametric cells in a library and use them from the IPKISS Link for Siemens EDA environment or in an IPKISS python code design.

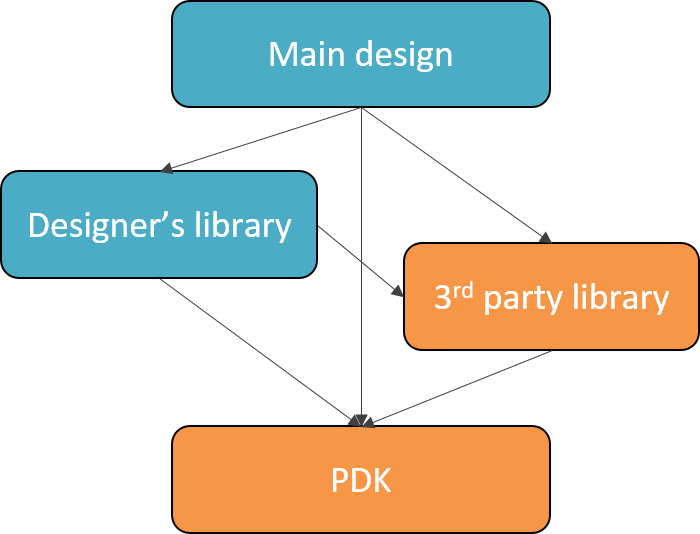

Use case: Using internal and 3rd party libraries

In a larger design team or in the case of consecutive design projects, a designer or a design team will typically build up their own library of subcircuits that perform specific reusable functions. Using Luceda’s software, the designer or design team can create such proprietary libraries that work together with the Luceda PDK for CORNERSTONE SiN. These re-usable libraries can then be shared within the team, outside of the company or used in consecutive projects.

The designer can in this way embed and sustain design knowledge in a library, and base a new design both on the PDK as well as these internal libraries.

One step further, a designer can also acquire 3rd party libraries and use them in a design project in the same way.

Fig. 2 Designing with reuseable design libraries and a PDK.

Getting Started

This section explains how to load the PDK in IPKISS and basics of how to use it.

If you are unfamiliar with Luceda IPKISS, please have a look at the IPKISS documentation and samples. The documentation and samples are available from the IPKISS Control Center.

The latest IPKISS documentation is also available online at http://docs.lucedaphotonics.com/index.html.

Extracting the PDK

The PDK is distributed as a zip file, which you can extract with the unzip utility of your choice (unzip, WinZip, 7-zip, …).

For the purpose of this manual, we assume you have unzipped “cornerstone_sin-1.1.luceda3.zip” as C:\temp\cornerstone_sin.

You can inspect the directory structure of the PDK:

data/: Contains GDS files of some fixed cells

docs/: Contains this file

docs/examples/scripts: Example IPKISS python scripts

docs/examples/lib.defs: Example of IPKISS Link for Siemens EDA design project

ipkiss/: IPKISS technology, pcells, models and functions (Python)

ipkiss/conerstone_sin/cornerstone_sin.iclib: Symbol library for the PDK (IPKISS Canvas)

openaccess/: Design libraries

openaccess/cornerstone_sin/: OpenAccess database for the PDK (L-Edit)

techfiles/: Tech files (layers, display) for various tools

techfiles/klayout/: Layer settings for KLayout GDSII visualization

Using the PDK with IPKISS Link for Siemens EDA

You can follow the instructions given in our documentation https://docs.lucedaphotonics.com/links/ipkisseda/ledit/tutorial_pdk_based_circuit/.

Using the PDK with IPKISS

Setting up the editor environment

You can follow the instructions given in our documentation https://docs.lucedaphotonics.com/tutorials/environment_setup/create_project_pdk

Examples

The PDK comes bundled with a series of examples for use in IPKISS, in the C:\temp\cornerstone_sin\docs\examples\scripts folder. These are executable Python files. The examples are a good starting point to learn how to design with the Luceda PDK for CORNERSTONE SiN. Below is a summary of the shipped examples:

Example name

Description

example_layers.py

Visualize all the layers that are available in the cornerstone_sin technology

example_waveguides.py

Visualize the waveguides available in the cornerstone_sin technology

example_heater.py

Example of a waveguide with a heater filament

example_mzi.py

Example of MZI circuit exported to IPKISS Canvas

example_design_passive.py

Example of a parameter sweep of ring resonators with automated fiber coupler embedding

example_customcell.py

Create a custom PCell in IPKISS using the CORNERSTONE SiN technology

example_phc_sin300.py

Example of a photonic crystal component using the Luceda picazzo3 library for 300nm platform

example_components_300.py

Shows the PDK components for 300nm platform

References

IPKISS documentation: http://docs.lucedaphotonics.com/index.html

Library organization: https://docs.lucedaphotonics.com/links/ipkisseda/libraries/library_organization/

Technology settings

The PDK contains layer definitions and virtual fabrication settings for the 300nm SiN process. Refer to the CORNERSTONE SiN design rule manual and MPW call documents for detailed information.

Layers

The following table gives an overview of the available layers and how they are named in Ipkiss. See the CORNERSTONE SiN design rules manual for further information about the layers defined by CORNERSTONE.

Layer name |

Description |

IPKISS Layer |

GDS Number |

|---|---|---|---|

WG |

Silicon Etch - Waveguides (Light field) |

TECH.PPLAYER.WG |

203/0 |

WG_HOL |

Silicon Etch - Waveguides (Dark field) |

TECH.PPLAYER.WG_HOL |

204/0 |

HT |

Heater Filaments |

TECH.PPLAYER.HT |

39/0 |

PAD |

Heater Contact Pads |

TECH.PPLAYER.PAD |

41/0 |

CELL |

Cell Outline |

TECH.PPLAYER.NONE.CELL |

99/0 |

LBL |

Label - DRC purpose layer then included in GDS 4 |

TECH.PPLAYER.NONE.LBL |

100/0 |

STRIP_TRACE |

Strip waveguide routing - Luceda non-tapeout layer |

TECH.PPLAYER.STRIP_TRACE |

Components

Which components are available to use from the Luceda PDK for CORNERSTONE SiN?

The Luceda PDK for CORNERSTONE SiN contains a number of predefined components that have been tested by the fab, as well as predefined waveguide templates. In addition, Luceda has provided a number of parametric cells to make life of a designer easier.

Users can use these components and mix them with their own custom designed components to create larger circuits.

How to use Luceda PDK for CORNERSTONE SiN components?

An example of how to instantiate (or place) PDK components in IPKISS, you may refer the sample located at:

<path_to_installed_PDK>\cornerstone_sin\docs\examples\scripts\example_components.py

For 300nm SiN, refer to the example at <path_to_installed_PDK>\cornerstone_sin\examples\scripts\example_components_300.py

With IPKISS, you may execute the sample Python code. In order to learn how to execute an IPKISS code, please refer to section IPKISS.

If you use IPKISS Link for Siemens EDA, you will be able to use your mouse to drag-and-drop the components in L-Edit. The explanation can be found in section IPKISS Link for Siemens EDA.

Waveguide template components

Waveguide trace templates are used to define how the connecting waveguides between the devices should be like. It contains the technology information on the layers and geometrical drawing of a specific type of waveguide, such as wire or rib waveguides.

Using the waveguide trace template, when users define the waveguide type at a device port and the connection line with another device, the waveguide will be generated with the corresponding waveguide type at the port it connects to. There are also devices that are drawn using the waveguide template as a layout parameter. It is useful in this case to change the device design by updating the waveguide template.

One waveguide template is predefined in the PDK: StripWaveguideTemplate, for strip waveguides fully etched to the BOX.

Luceda picazzo components

Besides the component library provided by the foundry, users are also able to use the component templates from IPKISS’ Picazzo library.

Note

Unlike the Luceda PDK for CORNERSTONE SiN components of which device performance is characterized and guaranteed by the fab, the Picazzo library components are up to the user to ensure compatibility with the design rules and the designed device manufacturability and performance.

The list of Picazzo library components and their documentation can be found in the IPKISS manual: https://docs.lucedaphotonics.com/picazzo/

In the documentation examples, we use the silicon_photonics as the technology library (a demo technology library from IPKISS). Now that we have a real-world PDK, we are able to use it as the technology library for the picazzo design.

Photonic crystals

Picazzo offers a lot of components for drawing photonic crystals: https://docs.lucedaphotonics.com/picazzo/phc/ These however need some customization in order to work with CORNERSTONE SiN: the SiN slab area needs to be explicitly added.

For 300nm SiN, an example is in <path_to_installed_PDK>\docs\examples\scripts\example_phc_sin300.py.

How to customize a component design?

Users can also choose start a component design from scratch, instead of starting from a CORNERSTONE SiN library component or picazzo library component.

An example is given in <path_to_installed_PDK>\docs\examples\scripts\example_customcell.py.

Component List

Grating Couplers

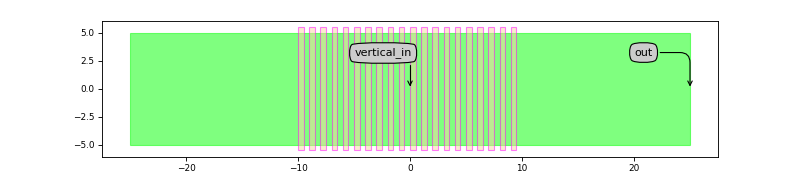

STRIP_Grating_Coupler

PCell for Grating Coupler in strip waveguide

- Parameters:

- inclination: float

out-of-plane angle of the grating coupler

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- grating: PCell, locked

- socket: PCell, locked

- trace_template: PCell and _TraceTemplate, locked

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

out |

Optical |

(25.0,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

vertical_in |

Optical |

(0.0,0.0) |

180.0 |

90.0 |

Layout

Parameters

socket_width: float and number > 0 line_length: float and number > 0

length of the grating trenches (perpendicular to the socket waveguide)

- line_width: float and number > 0

width of the grating trenches, drawn in the given layer

- n_o_periods: int and number > 0

number of periods of the grating

- origin: Coord2

local origin of the grating (first trench)

- period: float and number > 0

period of the grating

- socket_length: float and number > 0

length of the straight waveguide socket

CircuitModel

Parameters

- bandwidth_xdB: float and number > 0

xdB bandwidth [um]

- center_wavelength: float and number > 0

center wavelength [um]

- peak_IL_dB: float and number > 0

peak insertion loss [dB]

- reflection: Number, number, complex

Complex reflection back into the waveguide

- reflection_vertical: Number, number, complex

Complex reflection back into the vertical direction

- xdB: float and number > 0

x at which the bandwidth is given [dB]

300 nm SiN cells

SiN300nm_1550nm_TE_STRIP_Grating_Coupler

TE C-band strip grating coupler.

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

out |

Optical |

(225.0,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

vertical_in |

Optical |

(0.0,0.0) |

180.0 |

90.0 |

SiN300nm_1310nm_TE_STRIP_Grating_Coupler

TE O-band strip grating coupler.

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

out |

Optical |

(227.5,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

vertical_in |

Optical |

(0.0,0.0) |

180.0 |

90.0 |

Multi Mode Interferometers

Parametric cells

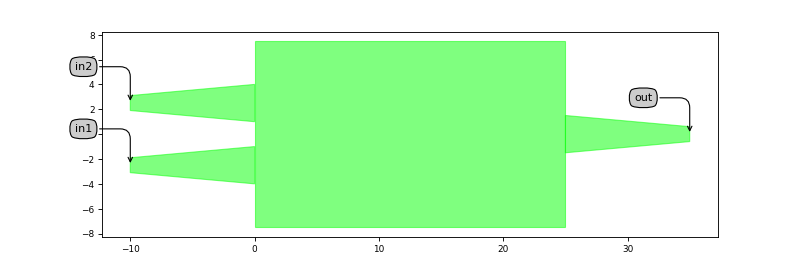

STRIP_2x1_MMI

PCell for 2x1 MMI in strip waveguide

- Parameters:

- transition_database: AutoTransitionDatabase

AutoTransitionDatabase in which the correct transition between the two trace templates can be looked up.

- port_labels: ( List with type restriction, allowed types: <class ‘str’> ), *None allowed*

Labels of the ports to be processed. Set to None to process all ports.

- external_port_names: str

Dictionary for remapping of the port names of the contents to the external ports

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- input_trace_template: PCell and _TraceTemplate, locked

- mmi_trace_template: PCell and _TraceTemplate, locked

- output_trace_template: PCell and _TraceTemplate, locked

- trace_template: PCell and _TraceTemplate, locked

- transitions: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

- n_inputs: int and number > 0, locked

Number of input channels.

- n_outputs: int and number > 0, locked

Number of output channels.

- input_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

List of the input trace templates.

- output_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

List of the output trace templates.

- contents: PCell, locked

Contains the base MMI without the tapers

- mmi_trace: PCell, locked

Trace of the MMI section

- trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

list of templates to apply to all ports

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-10.0,-2.5) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-10.0,2.5) |

180.0 |

StripWaveguideTemplate |

0.0 |

out |

Optical |

(35.0,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

Layout

Parameters

- port_width: float and number > 0

Width of port [um]

- taper_width: float and number > 0

Width of taper [um]

- mmi_width: float and number > 0

Width of the MMI [um]

- trace_spacing: float and Real, number and number >= 0

Offset between the traces at the input and the output

- length: float and number > 0

Length of the MMI

- transition_length: ( float and Real, number and number >= 0 ), None allowed

Length of the transition. Set to None to take the standard transition length.

CircuitModel

Parameters

- insertion_loss_dB: float and number > 0

Loss based on sum of outputs [dB]

- power_imbalance_dB: float

Power difference between the output ports [dB]

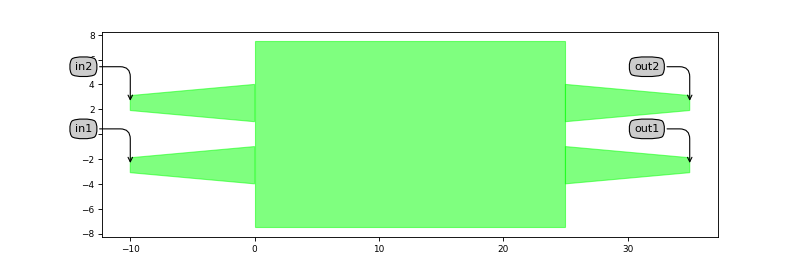

STRIP_2x2_MMI

PCell for 2x2 MMI in strip waveguide

- Parameters:

- transition_database: AutoTransitionDatabase

AutoTransitionDatabase in which the correct transition between the two trace templates can be looked up.

- port_labels: ( List with type restriction, allowed types: <class ‘str’> ), *None allowed*

Labels of the ports to be processed. Set to None to process all ports.

- external_port_names: str

Dictionary for remapping of the port names of the contents to the external ports

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- input_trace_template: PCell and _TraceTemplate, locked

- mmi_trace_template: PCell and _TraceTemplate, locked

- output_trace_template: PCell and _TraceTemplate, locked

- trace_template: PCell and _TraceTemplate, locked

- transitions: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

- n_inputs: int and number > 0, locked

Number of input channels.

- n_outputs: int and number > 0, locked

Number of output channels.

- input_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

List of the input trace templates.

- output_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

List of the output trace templates.

- contents: PCell, locked

Contains the base MMI without the tapers

- mmi_trace: PCell, locked

Trace of the MMI section

- trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

list of templates to apply to all ports

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-10.0,-2.5) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-10.0,2.5) |

180.0 |

StripWaveguideTemplate |

0.0 |

out1 |

Optical |

(35.0,-2.5) |

0.0 |

StripWaveguideTemplate |

0.0 |

out2 |

Optical |

(35.0,2.5) |

0.0 |

StripWaveguideTemplate |

0.0 |

Layout

Parameters

- port_width: float and number > 0

Width of port [um]

- taper_width: float and number > 0

Width of taper [um]

- mmi_width: float and number > 0

Width of the MMI [um]

- trace_spacing: float and Real, number and number >= 0

Offset between the traces at the input and the output

- length: float and number > 0

Length of the MMI

- transition_length: ( float and Real, number and number >= 0 ), None allowed

Length of the transition. Set to None to take the standard transition length.

CircuitModel

Parameters

- insertion_loss_dB: float and number > 0

Loss based on sum of outputs [dB]

- power_imbalance_dB: float

Power difference between the output ports [dB]

300 nm SiN cells

SiN300nm_1550nm_TE_STRIP_2x1_MMI

C-band 50/50 splitting 2x1 MMI

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-50.0,-2.9) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-50.0,2.9) |

180.0 |

StripWaveguideTemplate |

0.0 |

out |

Optical |

(114.7,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

SiN300nm_1550nm_TE_STRIP_2x2_MMI

C-band 50/50 splitting 2x2 MMI

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-50.0,-3.05) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-50.0,3.05) |

180.0 |

StripWaveguideTemplate |

0.0 |

out1 |

Optical |

(282.0,-3.05) |

0.0 |

StripWaveguideTemplate |

0.0 |

out2 |

Optical |

(282.0,3.05) |

0.0 |

StripWaveguideTemplate |

0.0 |

SiN300nm_1310nm_TE_STRIP_2x1_MMI

O-band 50/50 splitting 2x1 MMI

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-30.0,-2.0) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-30.0,2.0) |

180.0 |

StripWaveguideTemplate |

0.0 |

out |

Optical |

(72.0,0.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

SiN300nm_1310nm_TE_STRIP_2x2_MMI

O-band 50/50 splitting 2x2 MMI

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-30.0,-2.1) |

180.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(-30.0,2.1) |

180.0 |

StripWaveguideTemplate |

0.0 |

out1 |

Optical |

(156.0,-2.1) |

0.0 |

StripWaveguideTemplate |

0.0 |

out2 |

Optical |

(156.0,2.1) |

0.0 |

StripWaveguideTemplate |

0.0 |

Ring Filters

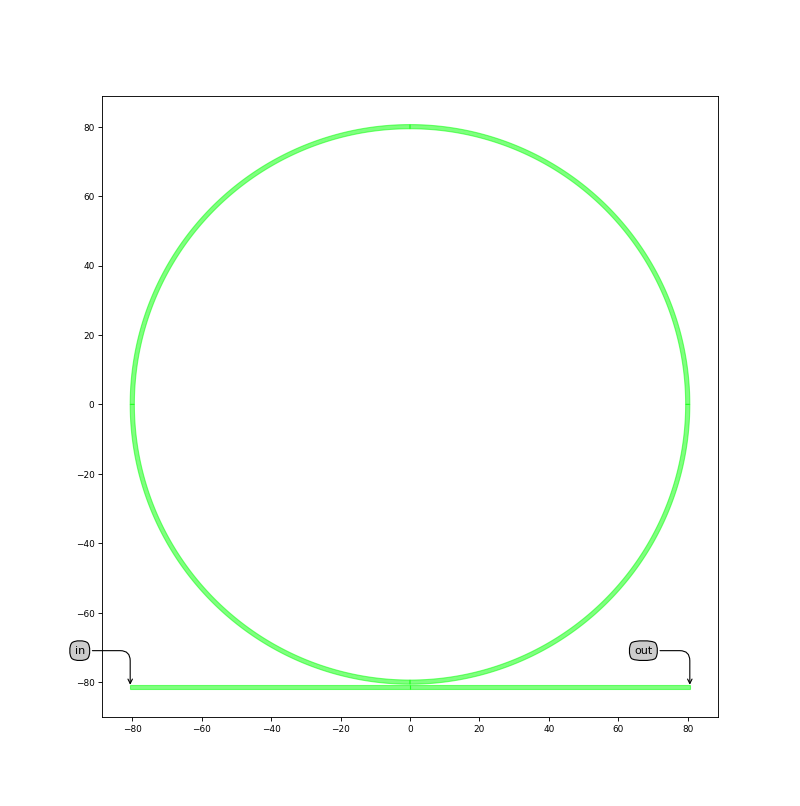

STRIP_AllPass_Ring

PCell for All-Pass Ring filter in strip waveguide

- Parameters:

- coupler_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of trace_templates for the ring couplers. By default the same template as the ring is taken

- ring_trace_template: PCell and _WaveguideTemplate

Trace template for the ring waveguide

- couplers: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of coupler PCells

- ring_segments: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of Ring PCells

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- ring_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

Trace templates for the ring segments. Locked, as there is only one segment in this Ring. Use ‘ring_trace_template’ instead.

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in |

Optical |

(-80.6,-81.4) |

180.0 |

StripWaveguideTemplate |

0.0 |

out |

Optical |

(80.6,-81.4) |

0.0 |

StripWaveguideTemplate |

0.0 |

Layout

Parameters

- coupler_length: float and Real, number and number >= 0

Straight coupling part length [um]

- coupler_spacing: float and number > 0

Centerline-to-centerline spacing of the coupler [um]

- ring_length: float and number > 0

Total ring length (min of 2 * (pi*bend_radius + coupler_length))[um]

- width: float and number > 0

Width of the waveguide [um]

- bend_radius: float and number > 0

Bend radius for the auto-generated bends.

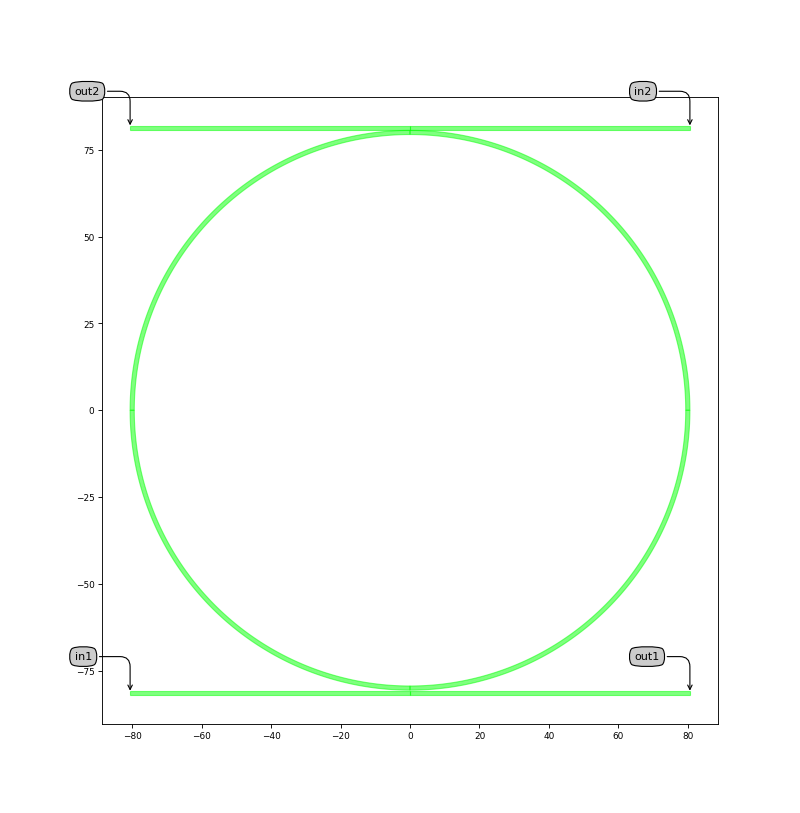

STRIP_AddDrop_Ring

PCell for Add-Drop Ring filter in strip waveguide

- Parameters:

- coupler_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of trace_templates for the ring couplers. By default the same template as the ring is taken

- ring_trace_template: PCell and _WaveguideTemplate

Trace template for the ring waveguide

- couplers: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of coupler PCells

- ring_segments: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

list of Ring PCells

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- ring_trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

Trace templates for the ring segments. Locked, as there is only one segment in this Ring. Use ‘ring_trace_template’ instead.

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in1 |

Optical |

(-80.6,-81.4) |

180.0 |

StripWaveguideTemplate |

0.0 |

out1 |

Optical |

(80.6,-81.4) |

0.0 |

StripWaveguideTemplate |

0.0 |

in2 |

Optical |

(80.6,81.4) |

0.0 |

StripWaveguideTemplate |

0.0 |

out2 |

Optical |

(-80.6,81.4) |

180.0 |

StripWaveguideTemplate |

0.0 |

Layout

Parameters

- bottom_coupler_spacing: float and number > 0

Centerline-to-centerline spacing of the bottom coupler [um]

- coupler_length: float and Real, number and number >= 0

Straight coupling length [um]

- ring_length: float and number > 0

Total ring length (min of 2 * (pi*bend_radius + coupler_length))[um]

- top_coupler_spacing: float and number > 0

Centerline-to-centerline spacing of the top coupler [um]

- width: float and number > 0

Width of the waveguide [um]

- bend_radius: float and number > 0

Bend radius for the auto-generated bends.

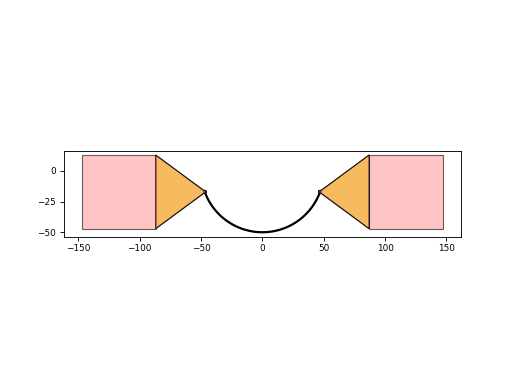

Heaters

A number of parametric cells are defined to assist the designer in creating heater filaments and metalization:

HeaterFilament

- Parameters:

- trace_template: PCell and ElectricalWireTemplate

(Source code, png, hires.png, pdf)

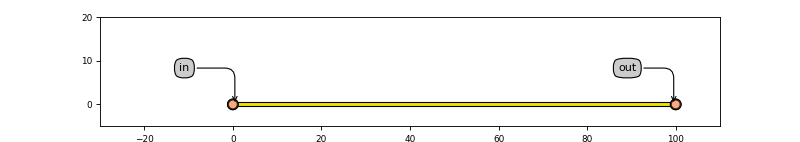

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in |

Electrical |

(0.45,0.0) |

None |

HeaterFilamentTemplate |

0.0 |

out |

Electrical |

(99.55,-0.0) |

None |

HeaterFilamentTemplate |

0.0 |

Layout

Parameters

- shape: Shape

Shape from which the Trace is calculated

Examples

import cornerstone_sin.all as cornerstone_lib

import ipkiss3.all as i3

from picazzo3.routing.place_route import PlaceComponents

filament = cornerstone_lib.HeaterFilament()

filament_sh = i3.ShapeArc(radius=50.0, start_angle=200.0, end_angle=340.0)

filament.Layout(shape=filament_sh)

contact_wedge = cornerstone_lib.HeaterWedge()

contact_wedge.Layout(end_width=60.0, length=40.0)

contact_pad = cornerstone_lib.HeaterPad()

contact_pad.Layout(height=60.0, width=60.0)

contacted_heater = PlaceComponents(

name="contacted_heater",

child_cells={

"filament": filament,

"wedge_west": contact_wedge,

"wedge_east": contact_wedge,

"pad_west": contact_pad,

"pad_east": contact_pad,

},

)

contacted_heater_lo = contacted_heater.Layout(

child_transformations={

"filament": (0.0, 0.0),

"wedge_west": i3.Rotation(rotation=180.0) + i3.Translation(filament_sh[0]),

"pad_west": filament_sh[0] - i3.Coord2((70.0, 0.0)),

"wedge_east": filament_sh[-1],

"pad_east": filament_sh[-1] + i3.Coord2((70.0, 0.0)),

}

)

contacted_heater_lo.visualize()

(Source code, png, hires.png, pdf)

StraightHeaterFilament

- Parameters:

- trace_template: PCell and ElectricalWireTemplate

(Source code, png, hires.png, pdf)

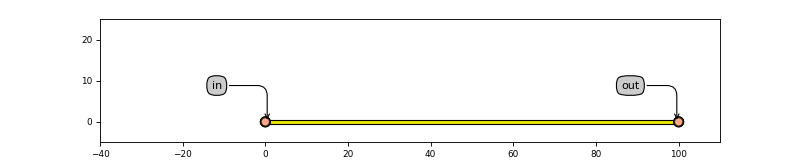

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in |

Electrical |

(0.45,0.0) |

None |

HeaterFilamentTemplate |

0.0 |

out |

Electrical |

(99.55,-0.0) |

None |

HeaterFilamentTemplate |

0.0 |

Layout

Parameters

- length: float and number > 0

Length of the heater filament [um]

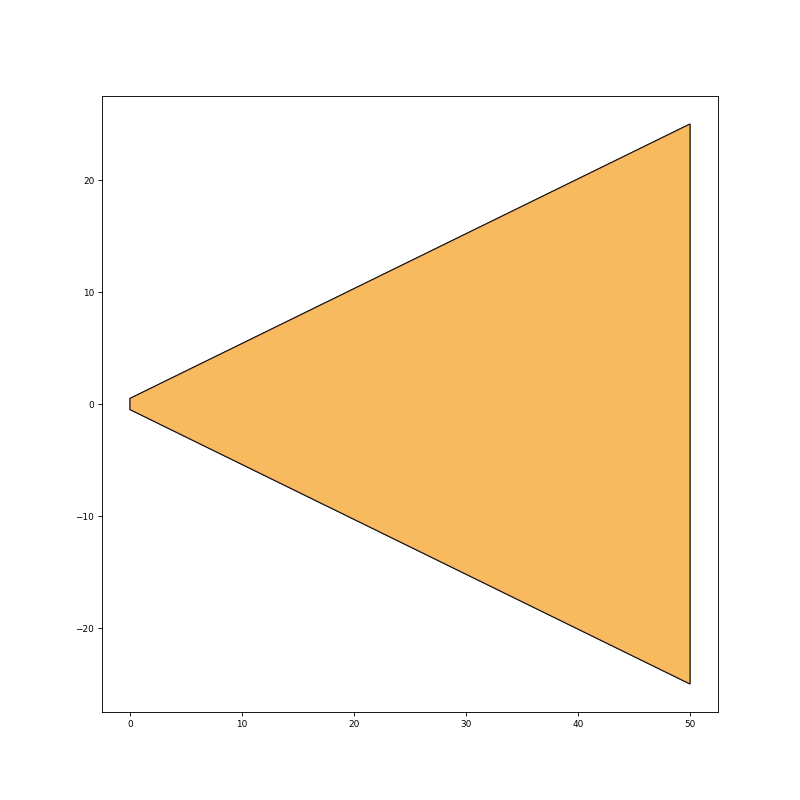

HeaterWedge

- Parameters:

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

(Source code, png, hires.png, pdf)

Layout

Parameters

- end_width: float and number > 0

End width of the Wedge [um]

- length: float and number > 0

Length of the Wedge [um]

- tip_width: float and number > 0

Tip width of the Wedge [um]

HeaterPad

- Parameters:

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

pad |

Electrical |

(0.0,0.0) |

None |

ElectricalWireTemplate |

0.0 |

Layout

Parameters

- height: float and number > 0

Height of the pad [um]

- width: float and number > 0

Width of the pad [um]

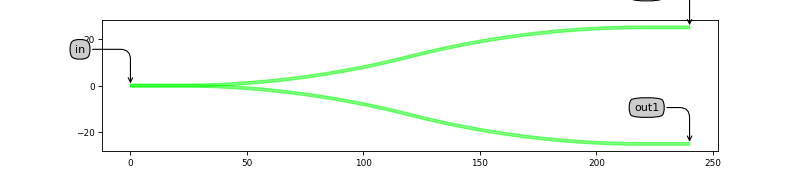

Y-Splitters

Ysplitter

PCell for Y-splitter in strip waveguide

- Parameters:

- trace_template: PCell and _WaveguideTemplate

Trace template of the Y-splitter (Strip by default)

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

(Source code, png, hires.png, pdf)

Ports

Name |

Type |

Position |

Angle |

Waveguide Template |

Inclination |

|---|---|---|---|---|---|

in |

Optical |

(0.0,0.0) |

180.0 |

StripWaveguideTemplate |

0.0 |

out1 |

Optical |

(240.0,-25.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

out2 |

Optical |

(240.0,25.0) |

0.0 |

StripWaveguideTemplate |

0.0 |

Layout

Parameters

- length: float and number > 0

Length of sbend [um]

- spacing: float and number > 0

Spacing between the outputs[um]

- straight_length: float and number > 0

Length of straight sections [um]

- width: float and number > 0

Width of the waveguide (only used if no trace_template provided) [um]