AutoTransitionPorts

- class picazzo3.container.transition_ports.AutoTransitionPorts

Pcell containing another PCell with transitions on all (labeled) ports, using AutoTraceTransitionFromPort. The target trace template is defined in

trace_template.- Parameters:

- trace_template: ( PCell and _WaveguideTemplate ), *None allowed*

Template for all ports, defaults to TECH.PCELLS.WG.DEFAULT.When set to None, the waveguide templates of the ports will be used.

- transition_database: AutoTransitionDatabase

AutoTransitionDatabase in which the correct transition between the two trace templates can be looked up.

- transitions: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>

Transitions (of type WaveguideTransitionFromPort) attached the the ports given in port_labels. Should be in the same order as port_labels.

- port_labels: ( List with type restriction, allowed types: <class ‘str’> ), *None allowed*

Labels of the ports to be processed. Set to None to process all ports.

- external_port_names: str

Dictionary for remapping of the port names of the contents to the external ports

- contents: PCell

the contents of the container: the child cell

- name: String that contains only ISO/IEC 8859-1 (extended ASCII py3) or pure ASCII (py2) characters

The unique name of the pcell

- Other Parameters:

- trace_templates: List with type restriction, allowed types: <class ‘ipkiss3.pcell.cell.pcell.PCell’>, locked

list of templates to apply to all ports

Examples

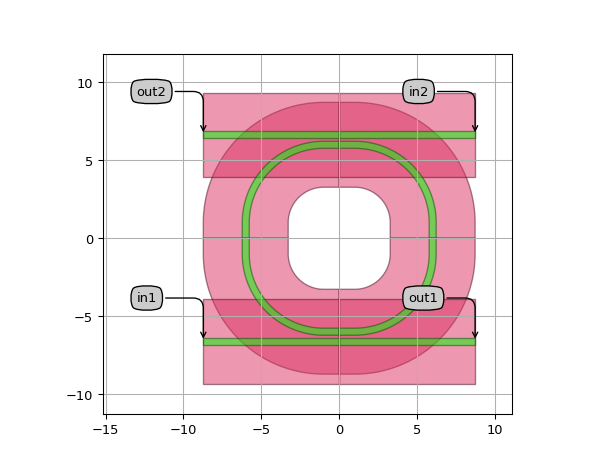

Tapering ports to a wider width:

import si_fab.all as pdk # noqa: F401 from picazzo3.filters.ring import RingRect180DropFilter my_ring = RingRect180DropFilter() my_ring.Layout() from picazzo3.container.transition_ports import AutoTransitionPorts wire_t = pdk.SiWireWaveguideTemplate() wire_t.Layout(core_width=0.7, cladding_width=0.7 + 2 * 2.0) my_ring_tapered_auto = AutoTransitionPorts( contents=my_ring, port_labels=["W0", "W1", "E0"], trace_template=wire_t ) my_ring_tapered_auto_layout = my_ring_tapered_auto.Layout() my_ring_tapered_auto_layout.visualize(annotate=True)

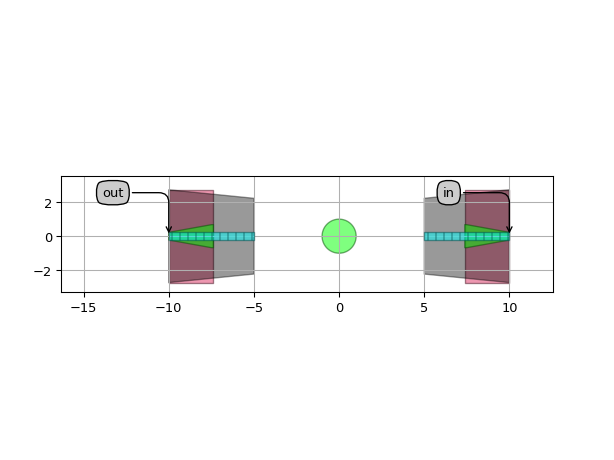

Using _transition_parameters:

import si_fab.all as pdk # noqa: F401 from picazzo3.traces.rib_wg import RibWaveguideTemplate from picazzo3.traces.wire_wg import WireWaveguideTemplate from picazzo3.container.transition_ports import AutoTransitionPorts import ipkiss3.all as i3 class MyCell(i3.PCell): class Layout(i3.LayoutView): def _generate_elements(self, elems): elems += i3.Circle(layer=i3.TECH.PPLAYER.SI) return elems def _generate_ports(self, ports): ports += i3.OpticalPort(name="in", position=(5.0, 0.0), trace_template=RibWaveguideTemplate()) ports += i3.OpticalPort( name="out", position=(-5.0, 0.0), angle=180, trace_template=RibWaveguideTemplate() ) return ports trace_template = WireWaveguideTemplate() auto_transition_ports = AutoTransitionPorts( contents=MyCell(), trace_template=trace_template, ) auto_transition_ports_lv = auto_transition_ports.Layout(_transition_parameters={"length": 5.0}) auto_transition_ports_lv.visualize(annotate=True)

Views

- class Layout

- Parameters:

- transition_length: ( float and int, float, integer, floating and number >= 0 ), *None allowed*

Length of the transition. Set to None to take the standard transition length.

- zero_length_if_identical:

uses a zero-length transition if the trace templates are identical

- flatten_transitions:

if true, flattens the transitions one level

- straight_extension: ( Coord2 and number >= 0 ), *None allowed*

Tuple: straight extensions of the transitions. Set to None to take the standard straight extensions

- contents_transformation: GenericNoDistortTransform

transformation to apply to the contents

- flatten_contents:

if True, it will insert the contents as elements in the layout, rather than as an Instance

- view_name: String that contains only alphanumeric characters from the ASCII set or contains _$. ASCII set is extended on PY3.

The name of the view

- Other Parameters:

- transition_lengths: locked